# SPIRAL and RF-PASS Three Dimensional Design and Analysis Tools for RF Integrated Circuits

By

Ersed Akcasu, Haris Basit,

Kerem Akcasu, Tufan Colak and Ibrahim Akcay

OEA International, Inc. 155 East Main Avenue Morgan Hill, CA 95037 www.oea.com

# **Acknowledgements**

Jerry Tallinger – OEA International, Inc.

Alla Toy – OEA International, Inc.

Onur Uslu - OEA International, Inc.

# **Agenda**

- Introduction to On-chip RF Components

- On-chip Inductors

- Why can not we use Pre-characterized Inductors

- Inductance Concepts

- Test Chip Results

- A Real Spiral Inductor Design

- Simplified "curve-fit" Model Generation

- On-chip Capacitor Designs

- Conclusions

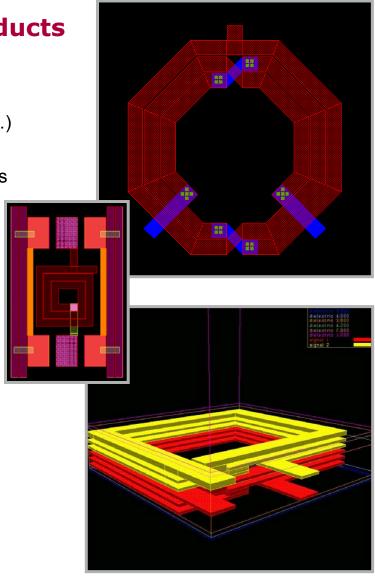

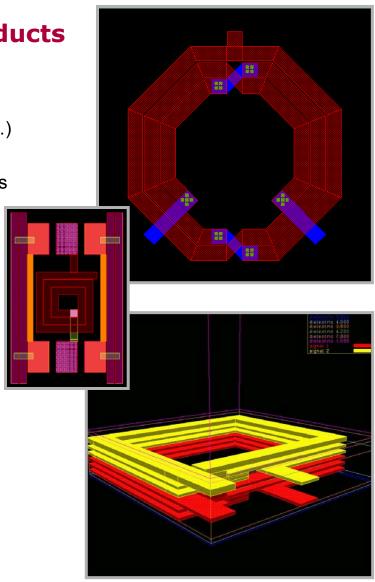

**OEA RF/Analog Software Products**

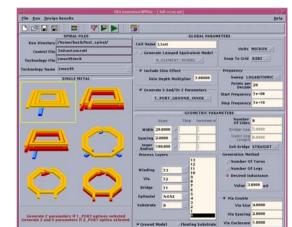

#### SPIRAL TM

- Includes all relevant effects (skin, substrate, etc...)

- Synthesizes a large variety of inductors

- Can examine thousands of designs in a few hours

- Generates layout, Spice, Z & S parameters

- Can fit to many simplified models

- Optimization engine included

#### RF-PASSTM

- Outputs N-Port Y, Z and S parameters

- Handles much more complex substrates and designs

- Optimization of arbitrarily complex passive structures

#### SUBSTRATE NOISE ANALYSIS

- Calculates full-chip substrate noise couplings

- Enables what-if exploration of isolation strategies

- Allows design planning before layout

#### **OEA RF/Analog Software Products**

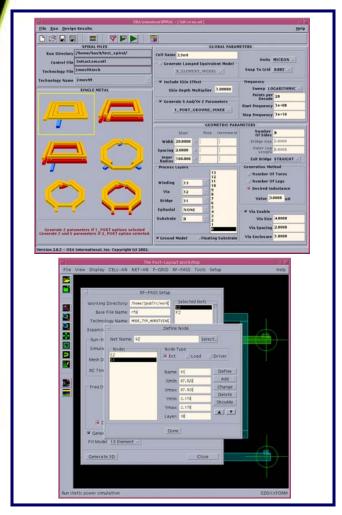

**OEA SPIRAL SPECIFIC PARAMETERS** Help Cancel SELECT SPIRAL SELECT ESCAPE = SPIRAL **ESCAPE** GPOL drawing 13 SPIRAL LAYER BRIDGE GAP 0 NDIFF drawing 12 VIA LAYER SELECT CHOICE PDIFF drawing 11 RUN MODE BRIDGE LAYER DESIRED INDUCTANCE NUMBER OF SIDES 100 NUMBER OF LEGS INNER RADIUS SPACING NUMBER OF TURNS 10 WIDTH Optional keywords. If used ALL three must be specified. OK Cancel VIA SIZE VIA SPACING 4 VIA ENCLOSURE 4 LIBRARY CELL NAME SPIRAL TECH FILE . /spiral/cmos99. techi BROWSE TECHNOLOGY /home/basit/SKILL/SPIRAL/ind **RUN DIR** OK Cancel SELECT UNITS SELECT SWEEP TYPE GROUND TYPE TARGET\_ONLY GROUND LAYER(S) 0 15 [ START FREQ. SNAP TO GRID 0.4 STOP FREQ.

**Generic UNIX Interfaces**

**Cadence Interface**

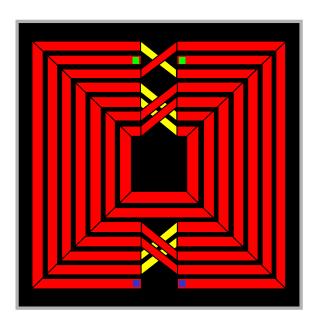

# Standard Inductors: 4 sided / 8 sided

- Usually uses top metal layer for winding

- Can use multiple metal layers in parallel

- Lowers series resistance

- Increases capacitance

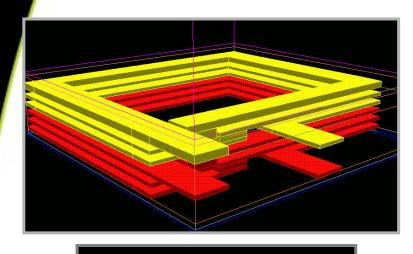

- Can use multiple metal layers in series (coil)

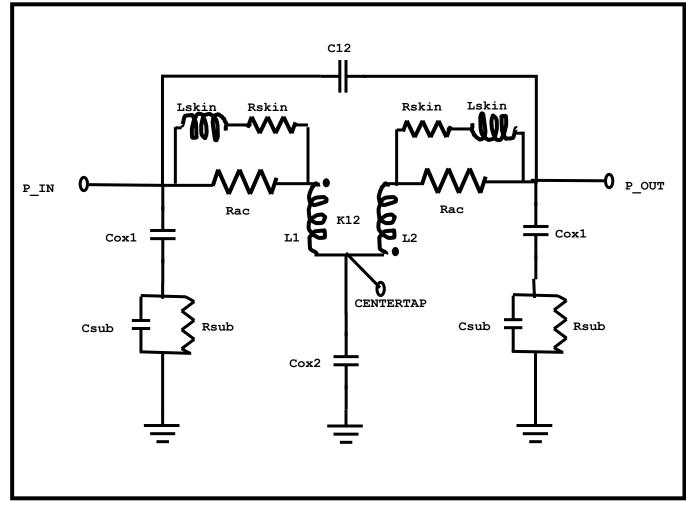

# **Symmetric Differential Inductors**

- Easily defined center tap

- Reduced chip area

- Higher Q (reduced substrate losses)

- No need to model parasitic coupling

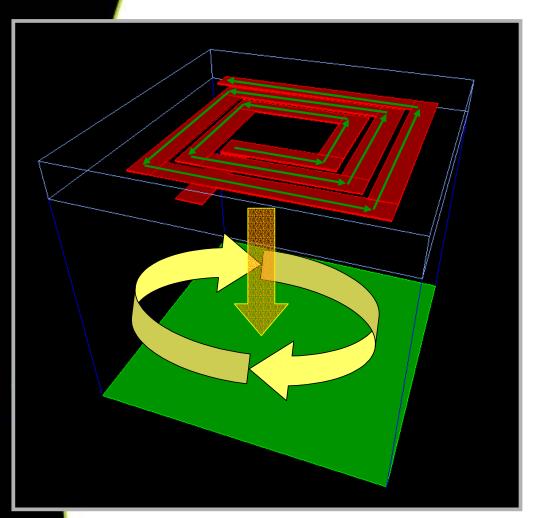

## **Transformers and Baluns**

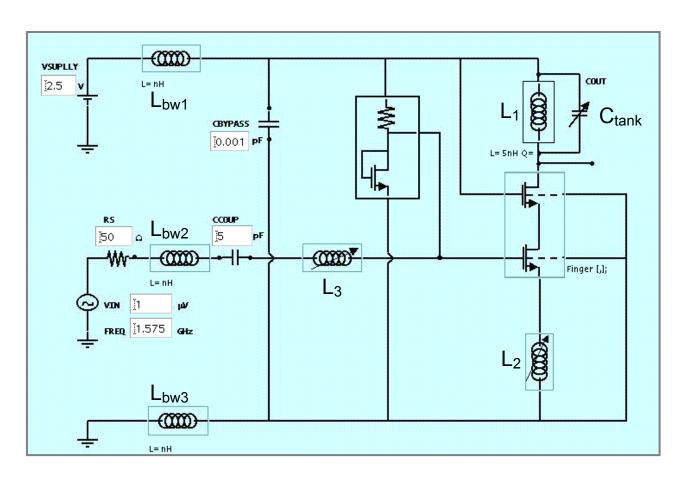

CMOS LNA Example to Show one can not use Pre-characterized Inductors for an Optimal Design!

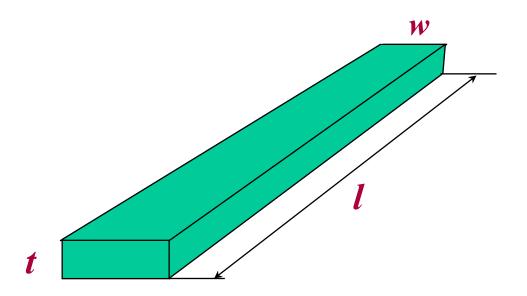

# **Inductance of a Rectangular Conductor**

$$L(\mu H) = 0.002l \left\{ \ln \left[ \frac{2l}{(w+t)} \right] + 0.5 - k \right\}$$

$$R(\Omega) = \frac{\delta l}{(w t)}$$

$$Z(j\omega) = R + j\omega L$$

Where  $\omega = 2\pi f$

Where k = f(w,t) 0 < k < 0.0025l,t,w in cm

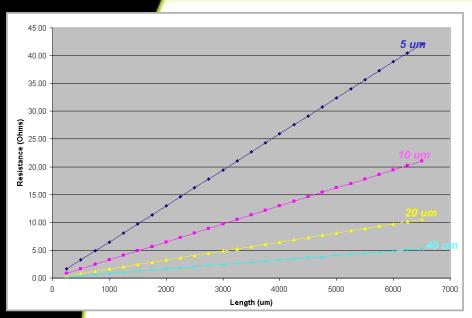

DC Resistance vs. Length at Various Widths (1 μm Thick Aluminum)

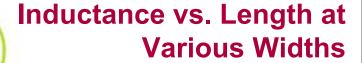

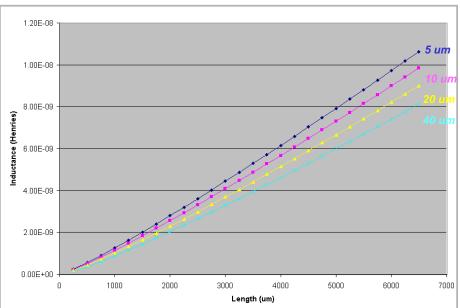

# Q and fpass of a Rectangular Conductors

$$\mathbf{Q} = \frac{\mathbf{I}_{\mathbf{m}}[\mathbf{Z}(j\omega)]}{\mathbf{R}\mathbf{e}[\mathbf{Z}(j\omega)]} = \frac{\mathbf{L}\omega}{\mathbf{R}} = \frac{\mathbf{L}2\pi f}{\mathbf{R}}$$

$$\mathbf{Q} = \frac{0.002wt \left[ \ln \left( \frac{2l}{w+t} \right) + 0.5 - k \right] \omega}{\delta}$$

$$Q = 1 \Longrightarrow f = \frac{R}{2\pi L}$$

$$f_{pass} = \frac{R}{2\pi L} = \frac{\delta}{0.002wt \left[ ln \left( \frac{2l}{w+t} \right) + 0.5 - k \right] 2\pi}$$

# Minimum Frequencies for Onset of Inductive Behavior

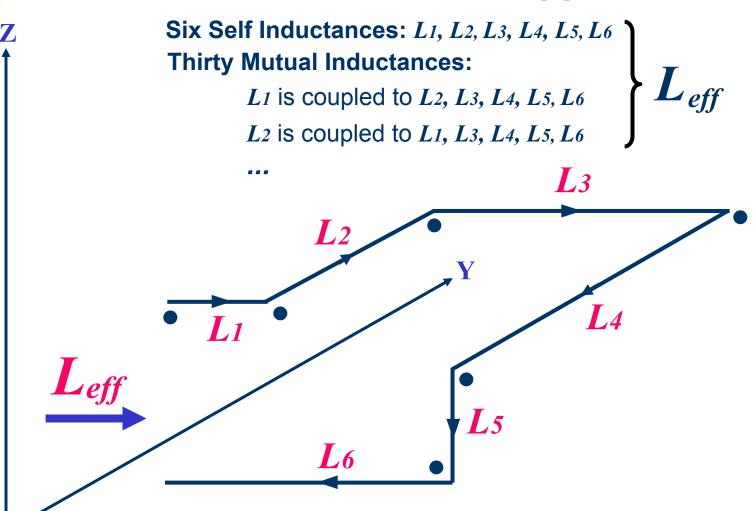

# **Partial Inductance Approach**

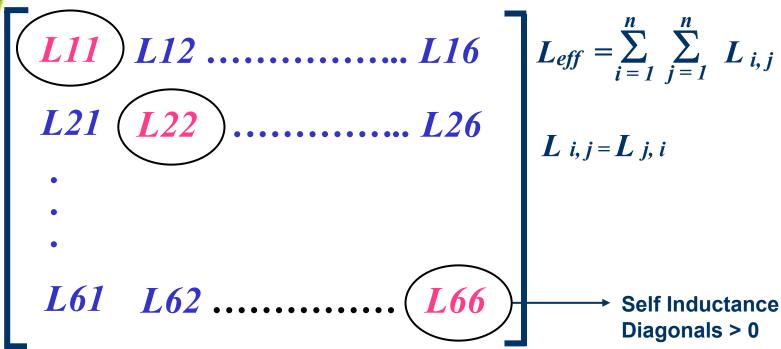

# **Inductance Matrix Representation**

Off Diagonals

Mutual Inductance

Can have < 0, > 0, or 0 value in Henry

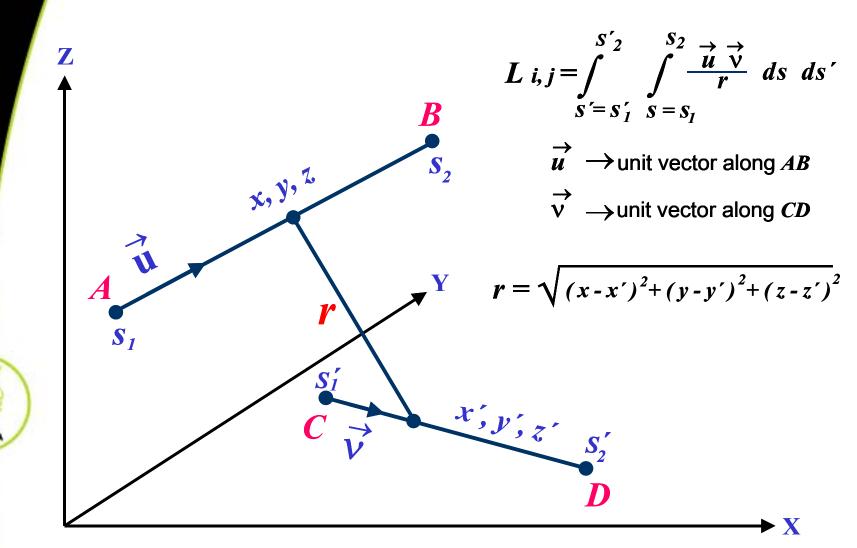

#### **Neumann Formulation of Mutual Inductance**

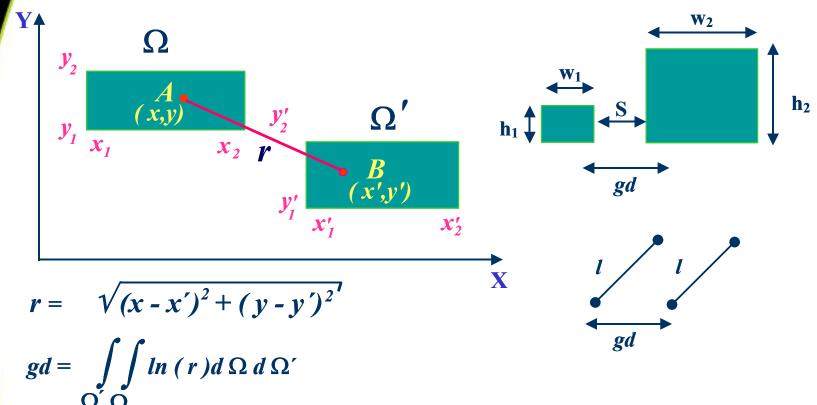

# **Geometric Distance Between Objects**

$$gd = \int_{v'=v_{1'}}^{y_{2'}} \int_{v=v_{1}}^{y_{2}} \int_{x'=x_{1'}}^{x_{2'}} \int_{x=x_{1'}}^{x_{2}}$$

$$gd = \int_{y'=y_{1'}}^{y_{2}} \int_{y=y_{1}}^{y_{2}} \int_{x'=x_{1'}}^{x_{2'}} \int_{x=x_{1}}^{x_{2}} \ln \sqrt{(x-x')^{2}+(y-y')^{2'}} dx dx' dy dy'$$

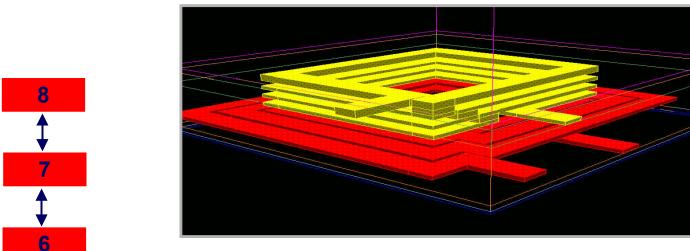

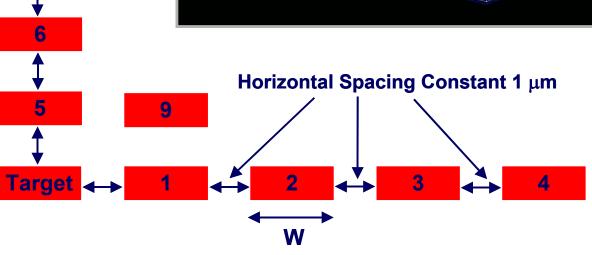

# **Inductive Coupling: Spirals and Helices**

Vertical Spacing Constant 1 μm

**Target and Nine Conductors are all the Same Width**

#### **Mutual Inductive Coupling as a Function of Width**

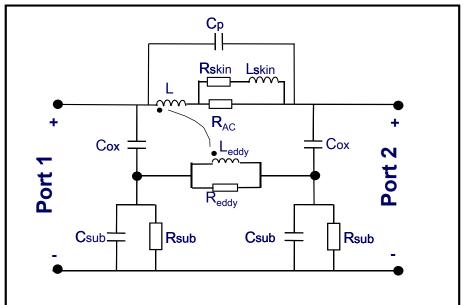

# **Detractors from Q**

Capacitive effects

Skin and Proximity effect in Conductors

Eddy and Displacement Currents in

Substrate

**Radiative Losses**

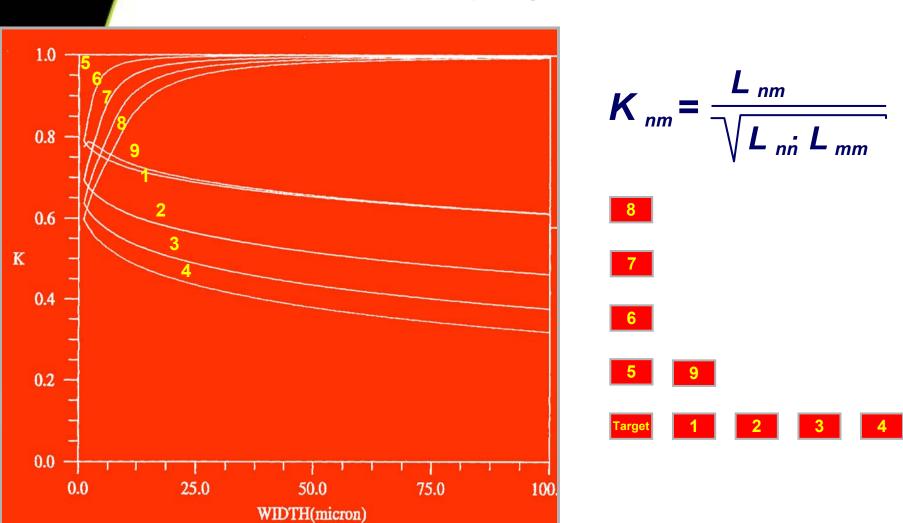

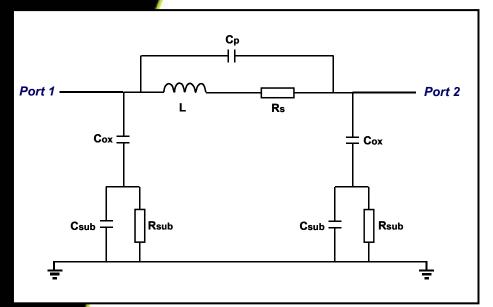

# **Simple Capacitance Model of an Inductor**

- Capacitance to Ground

- · Increases with width

- Increases with spacing

- Use highest metal level

- Capacitance between windings

- Less important for Si substrate

- Capacitance between winding and escape

- Capacitance within substrate

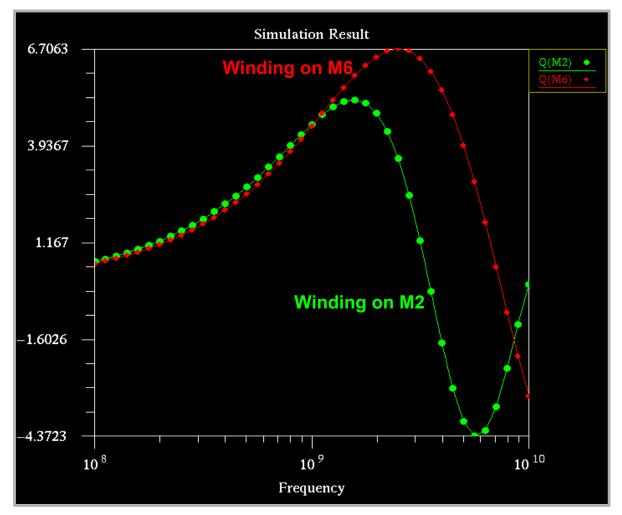

# **Q vs. Frequency for Two Inductors** (All metal layers have same thickness and $\rho$ )

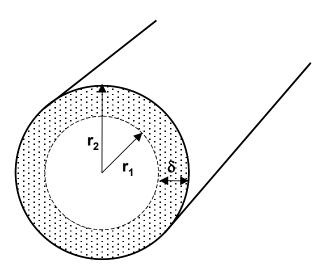

# **Skin Depth Area of a Conductor**

$$A_1 = \pi r_1^2$$

$A_2 = \pi r_2^2$

Skin Depth Area =  $A_2 - A_1 = \pi (r_2^2 - r_1^2)$

$$A_1 = w_1 h_1$$

$A_2 = w_2 h_2$

Skin Depth Area =  $A_2 - A_1 = w_2 h_2 - w_1 h_1$

$$\delta = \, r_2 \, \text{-} \, \, r_1$$

$$\delta = \sqrt{\frac{2}{\omega\mu\sigma}}$$

2

$$\delta = w_2 - w_1 = r_2 - r_1$$

RF current flow in shaded region

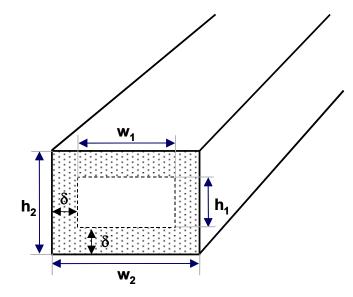

# **Skin Depth of Commonly Used Metals**

Depth (microns)

**Frequency (Hertz)**

## **Skin Effect in Conductors**

**Example shows currents in opposing directions.**

Low frequency currents are distributed across the entire cross sectional area to take path of minimum resistance.

High frequency currents are distributed to minimize mutual inductance thus minimizing impedance.

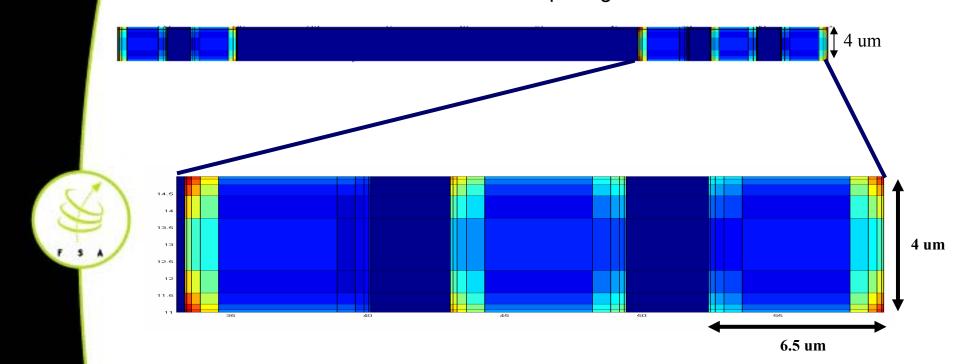

# **Current Distribution Due to Skin and Proximity Effects**

2.5 Turn Square Spiral100 um Inner Diameter6.5 um Width4 um Thickness2.1 um Spacing

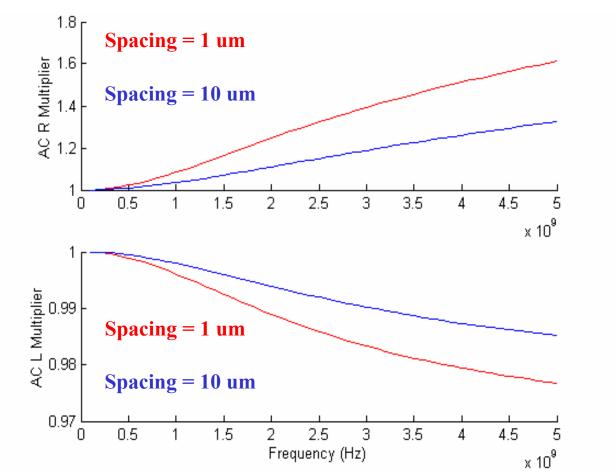

# AC Resistance & Inductance Comparison For 1um and 10um Spacing

# **Reducing Substrate Losses**

(Some Partially Useful Methods)

- Use high resistivity substrate

- Patterned shields

- Limited Use

- Significant Noise coupling

- Reduced operating frequency

- Depletion region

- Keep inductor small

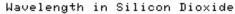

## **Radiative Losses**

- On chip inductors make very poor antennas

- No need to worry about radiation loss in most cases

- However, should be careful near quarter wavelength

V<sub>p</sub> = Propagation Velocity = Phase Velocity

$$V_p = 1/\sqrt{\mu\varepsilon} = 1/\sqrt{LC}$$

$$V_{p} = f\lambda$$

$$\lambda = (1/\sqrt{\mu\varepsilon}) / f$$

# Wavelength vs. Frequency in SiO<sub>2</sub>

Frequency

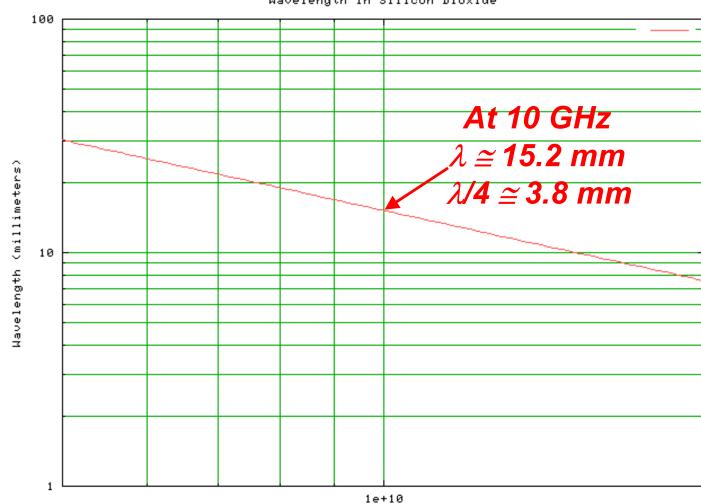

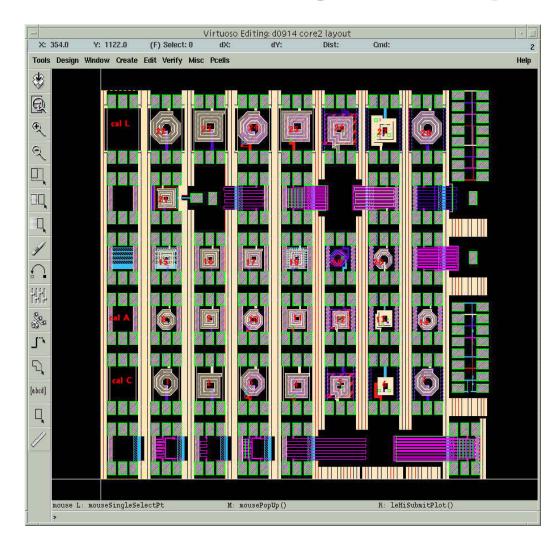

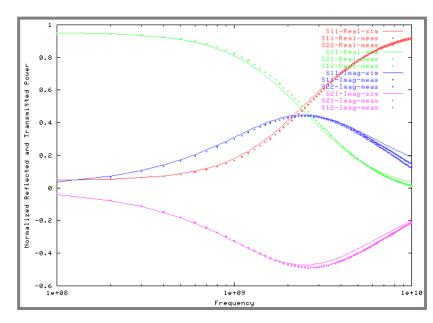

# **Validate Using Test Chips**

#### Measured vs Simulated ~ 1 nH

Measured vs Simulated ~ 7 nH

# A Real Design

# **Start with what Designer knows:**

- Physical Process Description

- Frequency Range or desired frequency

- Desired Inductance

- Minimum Acceptable Quality Factor

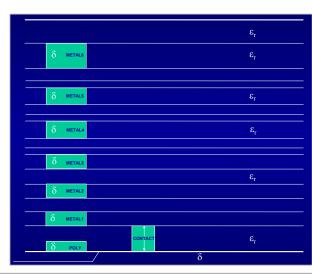

# **Process Technology File**

```

// spiral technology file:

technology CMOS

units microns

metal

-300.0

layer

0.1

//gnd

-1.0e+00

layer

-1.0

0

10

//epi

//met1

layer

1.2

1.7

3.3e-6

//via1

layer

1.7

2.3

6.0e-05

//met2

layer

2.3

2.8

3.3e-6

10

//via2

layer

11

2.8

3.4

6.0e-05

layer

12

3.4

3.9

3.3e-6

//met3

6.0e-05 //via3

layer

18

3.9

4.5

//met4

5.0

layer

19

4.5

3.3e-6

6.0e-05

//via4

layer

20

5.0

5.6

layer

21

5.6

6.5

3.3e-6

//met5

6.5

6.0e-05 //via5

layer

22

7.1

//met6

layer

23

7.1

9.2

3.3e-6

endmetal

dielectric

layer

10.0

//oxide

0.000

3.9

//nitride

layer

10,000

11.0

6.0

enddielectric

endtechnology

```

# A Real Inductor Design

## **Example Design Specification:**

- Frequency Range -- Example 2 GHz through 3 GHz

- Desired Inductance -- 3 nH

- Need Quality Factor > 8 @ 2.4 GHz

- Impedance at 2.4GHz = 2\*pi\*F\*L = 45 Ohms

# **An Aside: Three Definitions of Q**

Simplest Definition: (Zero at Resonance)

$$\frac{-\operatorname{Imag}(Y_{11})}{\operatorname{Real}(Y_{11})}$$

3-dB Bandwidth Definition:

$$\frac{\omega_{\circ}}{2} \frac{d\phi}{d\omega} \omega_{\circ}$$

Most General Definition

# A Real Design: Starting Questions

- What topology to use?

- Helix, spiral, symmetric, number of sides

- Which metal(s) to use for winding and bridge?

- Single metal, double metal, series or parallel metals

- What length, width and inner radius to use?

## **SPIRAL Control File**

```

CELL L3nH

TARGET ind

*GROUND LAYER 0 5

GROUND LAYER 0

PLANAR

UNITS MICRON

SOLVE

GROUND TYPE TARGET ONLY

*FLOAT

SKIN

1PORT

FREQUENCY LIN 2 2.4e+9

2.5e+9

SNAP TO GRID 0.05

```

```

SPIRAL ind

ESCAPE STRAIGHT

TYPE DOUBLE METAL

SIDE NUMBER 8

CHOICE L

DESIRED INDUCTANCE 3.0e-09

:-<) 8 52 4 (>-:

WIDTH

:-<) 2 10 2 (>-:

SPACING

INNER RADIUS :-<) 25 225 25 (>-:

BRIDGE GAP 3

SPIRAL LAYER 23

VIA LAYER 22

BRIDGE LAYER 21

ORIGIN 0.0 0.0

*VIA SIZE 2

*VIA SPACING 2

*VIA ENCLOSURE 1

ENDSPIRAL

```

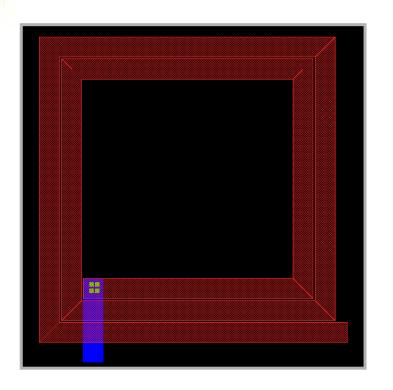

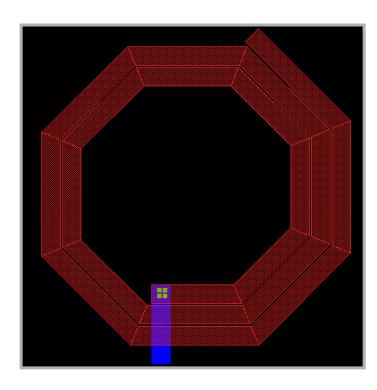

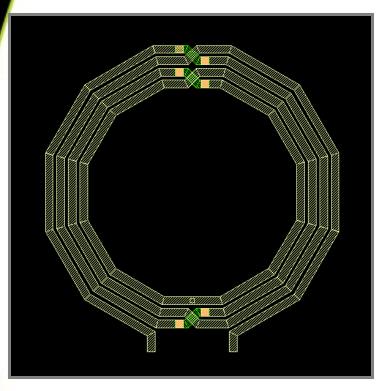

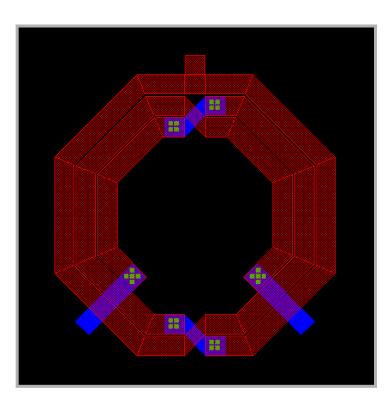

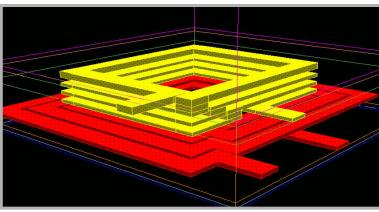

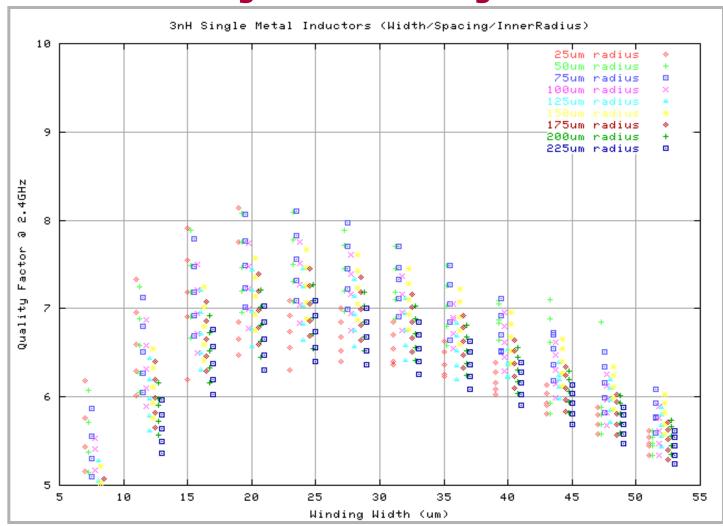

# **SPIRAL Output 3nH Single Metal - Octagon**

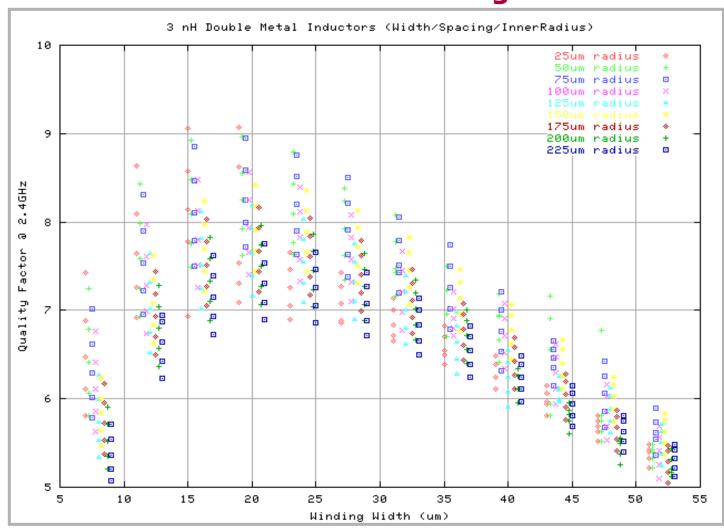

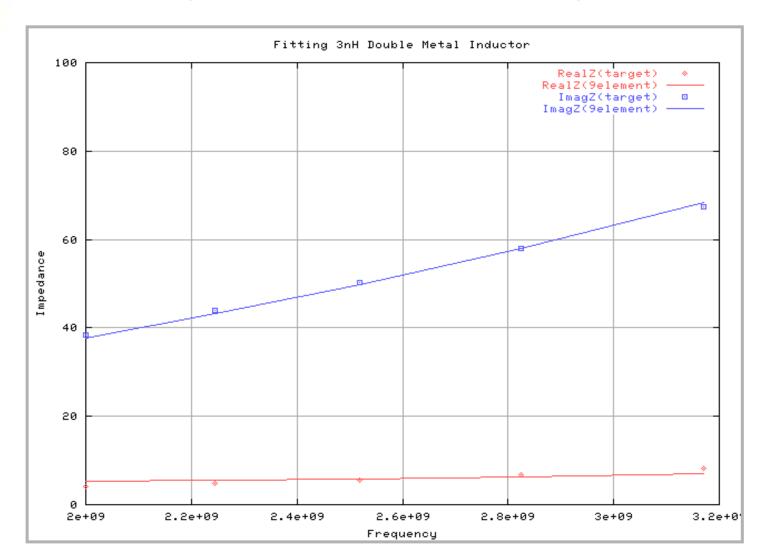

# **SPIRAL Output 3nH Double Metal - Octagon**

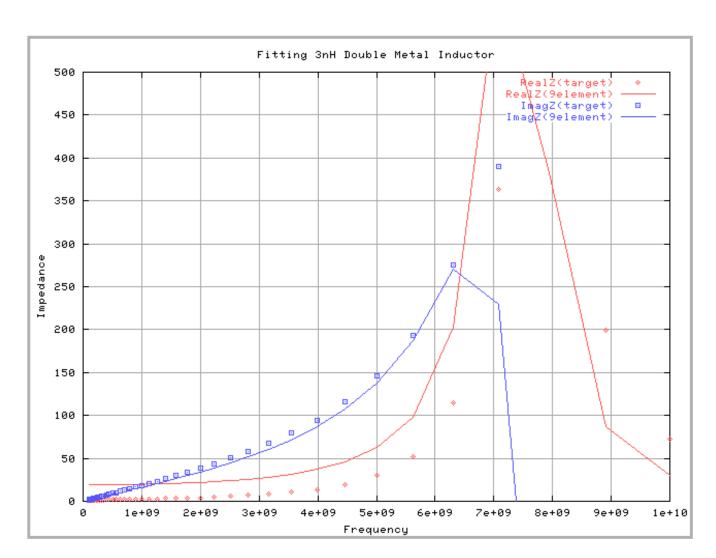

Model Fitting: Simple 9 Element Model

# Symmetric Inductor Lumped Model

## **SPIRAL Control File: Fitting**

```

CELL L3nH

TARGET ind

*GROUND LAYER 0 5

GROUND LAYER 0

PLANAR

UNITS MICRON

SOLVE

GROUND TYPE TARGET ONLY

*FLOAT

SKIN

1 PORT

FREQUENCY DEC 20 1e+8 10e+9

*FREQUENCY DEC 20 2e+9 3e+9

SNAP TO GRID 0.05

FIT MODEL9

*FIT MODEL13

*FIT SYMMETRIC

```

```

SPIRAL ind

ESCAPE STRAIGHT

TYPE DOUBLE METAL

SIDE NUMBER 8

CHOICE L

DESIRED INDUCTANCE 3.0e-09

WIDTH 20

SPACING 2

INNER RADIUS 25

BRIDGE GAP 3

SPIRAL LAYER 23

VIA LAYER 22

BRIDGE LAYER 21

ORIGIN 0.0 0.0

VIA SIZE 2

VIA SPACING 2

VIA ENCLOSURE 1

ENDSPIRAL

```

## **Narrow Band 9 Element Model Fit**

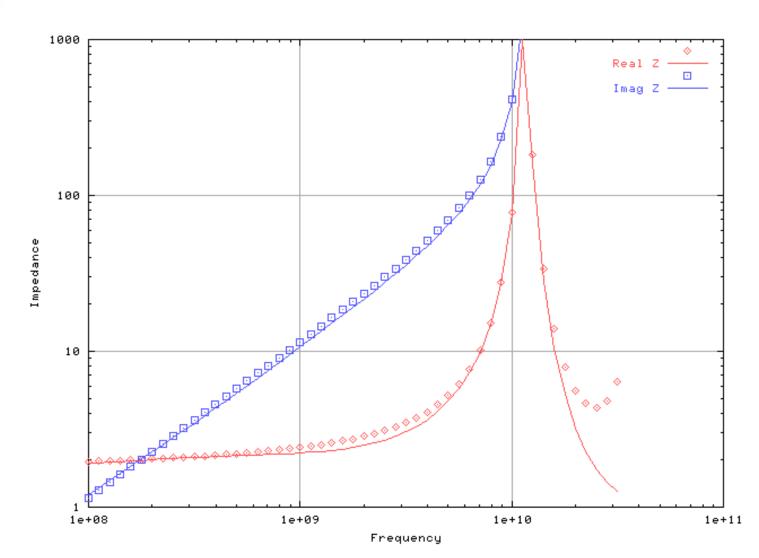

## **Broadband 9 Element Model Fit**

## **Broadband 13 Element Model Fit**

## **Resistive Components**

#### Thin Film Resistors (Not as Simple as they Look)

- Large Devices with Distributed Resistance and Capacitance

- Could Include Significant Substrate Effects

- Asymmetry Could Cause Noise Pickup from Substrate

- What is the coupling across segments?

- What is the coupling through the substrate?

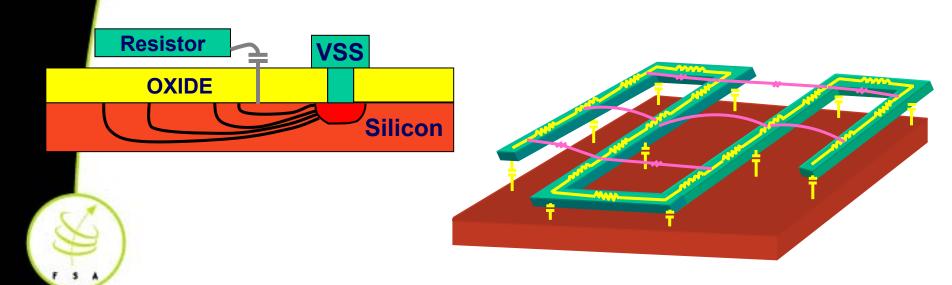

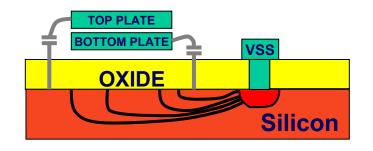

## **Capacitive Components**

#### MIM Capacitors

- Large distributed structures

- Asymmetric with respect to substrate

- OEA Patented technique

- Optimize Q, Capacitance Density, Parasitic Capacitance, etc...

- Symmetric relative to substrate (minimize noise pickup from substrate)

- Include skin and proximity effects

#### Control of undesired effects

- Minimize non-linear behavior

- Eliminate high resistance well contact

- Optimize selection and usage of metals

- Optimize finger width and spacing

- Optimize placement of metal straps

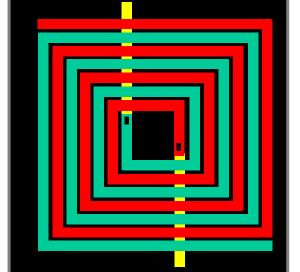

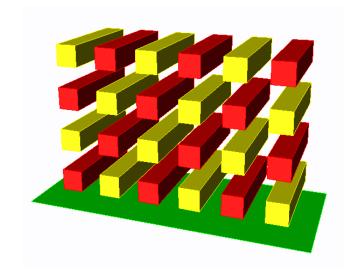

## **Multi-layer Interdigitated Capacitors**

| Finger<br>W/S(μ) | Finger<br>L (μ) | Capacitance<br>(fF) | Density<br>(fF/μ²) | Parasitic Cap (%) |

|------------------|-----------------|---------------------|--------------------|-------------------|

| 0.080            | 5.2             | 300                 | 9.70               | 1%                |

| 0.100            | 6.5             | 321                 | 6.64               | 1%                |

| 0.120            | 7.8             | 326                 | 4.69               | 1%                |

| 0.150            | 9.8             | 340                 | 3.13               | 2%                |

| 0.200            | 13.0            | 362                 | 1.87               | 3%                |

| 0.250            | 16.3            | 383                 | 1.27               | 4%                |

| 0.300            | 19.5            | 411                 | 0.95               | 5%                |

| 0.400            | 26.0            | 473                 | 0.61               | 8%                |

| 0.800            | 52.0            | 857                 | 0.28               | 14%               |

**OEA RF/Analog Software Products**

#### SPIRAL TM

- Includes all relevant effects (skin, substrate, etc...)

- Synthesizes a large variety of inductors

- Can examine thousands of designs in a few hours

- Generates layout, Spice, Z & S parameters

- Can fit to many simplified models

- Optimization engine included

#### RF-PASSTM

- Outputs N-Port Y, Z and S parameters

- Handles much more complex substrates and designs

- Optimization of arbitrarily complex passive structures

#### SUBSTRATE NOISE ANALYSIS

- Calculates full-chip substrate noise couplings

- Enables what-if exploration of isolation strategies

- Allows design planning before layout

## **Conclusions**

- Spiral Inductor Design is Not Simple as It Looks

- Selecting a Spiral from a Pre-characterized Library Does Not Do the Job!

- It is Possible to Design a Spiral or Group of Spiral Inductors Easily with the Right Software

- High Q and Very High Capacitance Design

Structures can be Designed to Save Valuable Chip

Real-estate by Using the Proper Tools